ആർട്ടിക്സ്-7 എഫ്പിജിഎ

കോർ ബോർഡ്

AC7A200

മൊഡ്യൂളിലെ സിസ്റ്റം

ഉപയോക്തൃ മാനുവൽ

പതിപ്പ് റെക്കോർഡ്

| പതിപ്പ് | തീയതി | റിലീസ് ചെയ്തത് | വിവരണം |

| റവ 1.0 | 28-06-20 | റേച്ചൽ ഷൗ | ആദ്യ റിലീസ് |

ഭാഗം 1: AC7A200 കോർ ബോർഡ് ആമുഖം

AC7A200 (കോർ ബോർഡ് മോഡൽ, ചുവടെയുള്ളത്) FPGA കോർ ബോർഡ്, ഇത് XILINX-ന്റെ ARTIX-7 സീരീസ് 100T XC7A200T-2FBG484I അടിസ്ഥാനമാക്കിയുള്ളതാണ്. ഉയർന്ന വേഗതയും ഉയർന്ന ബാൻഡ്വിഡ്ത്തും ഉയർന്ന ശേഷിയുമുള്ള ഉയർന്ന പ്രകടനമുള്ള കോർ ബോർഡാണിത്. അതിവേഗ ഡാറ്റാ കമ്മ്യൂണിക്കേഷൻ, വീഡിയോ ഇമേജ് പ്രോസസ്സിംഗ്, ഹൈ-സ്പീഡ് ഡാറ്റ ഏറ്റെടുക്കൽ തുടങ്ങിയവയ്ക്ക് ഇത് അനുയോജ്യമാണ്.

ഈ AC7A200 കോർ ബോർഡ് MICRON-ന്റെ MT41J256M16HA-125 DDR3 ചിപ്പിന്റെ രണ്ട് കഷണങ്ങൾ ഉപയോഗിക്കുന്നു, ഓരോ DDR-നും 4Gbit ശേഷിയുണ്ട്; രണ്ട് DDR ചിപ്പുകൾ 32-ബിറ്റ് ഡാറ്റാ ബസ് വീതിയിലേക്ക് സംയോജിപ്പിച്ചിരിക്കുന്നു, കൂടാതെ FPGA-യും DDR3-യും തമ്മിലുള്ള റീഡ്/റൈറ്റ് ഡാറ്റ ബാൻഡ്വിഡ്ത്ത് 25Gb വരെയാണ്; അത്തരം ഒരു കോൺഫിഗറേഷന് ഉയർന്ന ബാൻഡ്വിഡ്ത്ത് ഡാറ്റ പ്രോസസ്സിംഗിന്റെ ആവശ്യങ്ങൾ നിറവേറ്റാൻ കഴിയും.

AC7A200 കോർ ബോർഡ് 180V ലെവലിന്റെ 3.3 സ്റ്റാൻഡേർഡ് IO പോർട്ടുകളും 15V ലെവലിന്റെ 1.5 സ്റ്റാൻഡേർഡ് IO പോർട്ടുകളും 4 ജോഡി GTP ഹൈ സ്പീഡ് RX/TX ഡിഫറൻഷ്യൽ സിഗ്നലുകളും വികസിപ്പിക്കുന്നു. ധാരാളം IO ആവശ്യമുള്ള ഉപയോക്താക്കൾക്ക്, ഈ കോർ ബോർഡ് ഒരു നല്ല തിരഞ്ഞെടുപ്പായിരിക്കും. കൂടാതെ, FPGA ചിപ്പിനും ഇന്റർഫേസിനും ഇടയിലുള്ള റൂട്ടിംഗ് തുല്യ നീളവും ഡിഫറൻഷ്യൽ പ്രോസസ്സിംഗും ആണ്, കൂടാതെ കോർ ബോർഡിന്റെ വലുപ്പം 2.36 ഇഞ്ച് *2.36 ഇഞ്ച് മാത്രമാണ്, ഇത് ദ്വിതീയ വികസനത്തിന് വളരെ അനുയോജ്യമാണ്.

ചിത്രം 1-1: AC7A200 കോർ ബോർഡ് (മുൻവശം View)

ചിത്രം 1-2: AC7A200 കോർ ബോർഡ് (പിൻഭാഗം View)

ഭാഗം 2: FPGA ചിപ്പ്

മുകളിൽ സൂചിപ്പിച്ചതുപോലെ, ഞങ്ങൾ ഉപയോഗിക്കുന്ന FPGA മോഡൽ XC7A200T-2FBG484I ആണ്, ഇത് Xilinx-ന്റെ Artix-7 സീരീസിൽ പെടുന്നു. സ്പീഡ് ഗ്രേഡ് 2 ആണ്, താപനില ഗ്രേഡ് വ്യവസായ ഗ്രേഡ് ആണ്. ഈ മോഡൽ 484 പിന്നുകളുള്ള ഒരു FGG484 പാക്കേജാണ്. Xilinx ARTIX-7 FPGA ചിപ്പ് നാമകരണ നിയമങ്ങൾ താഴെ

ചിത്രം 2-1: ARTIX-7 സീരീസിന്റെ പ്രത്യേക ചിപ്പ് മോഡൽ നിർവ്വചനം

ചിത്രം 2-2: ബോർഡിൽ FPGA ചിപ്പ്

FPGA ചിപ്പ് XC7A200T യുടെ പ്രധാന പാരാമീറ്ററുകൾ ഇനിപ്പറയുന്നവയാണ്

| പേര് | പ്രത്യേക പാരാമീറ്ററുകൾ |

| ലോജിക് സെല്ലുകൾ | 215360 |

| കഷ്ണങ്ങൾ | 16-02-92 |

| CLB ഫ്ലിപ്പ്-ഫ്ലോപ്പുകൾ | 269200 |

| റാം (kb) തടയുക | 13140 |

| ഡിഎസ്പി സ്ലൈസുകൾ | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps എഡി |

| ജിടിപി ട്രാൻസ്സിവർ | 4 GTP, 6.6Gb/s പരമാവധി |

| സ്പീഡ് ഗ്രേഡ് | -2 |

| താപനില ഗ്രേഡ് | വ്യാവസായിക |

FPGA വൈദ്യുതി വിതരണ സംവിധാനം

ആർട്ടിക്സ്-7 FPGA പവർ സപ്ലൈസ് VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC, VMGTAVTT എന്നിവയാണ്. VCCINT എന്നത് FPGA കോർ പവർ സപ്ലൈ പിൻ ആണ്, അത് 1.0V-ലേക്ക് ബന്ധിപ്പിക്കേണ്ടതുണ്ട്; VCCBRAM എന്നത് FPGA ബ്ലോക്ക് റാമിന്റെ പവർ സപ്ലൈ പിൻ ആണ്, 1.0V-ലേക്ക് ബന്ധിപ്പിക്കുക; VCCAUX എന്നത് FPGA ഓക്സിലറി പവർ സപ്ലൈ പിൻ ആണ്, 1.8V ബന്ധിപ്പിക്കുക; VCCO ആണ് വാല്യംtagBANK0, BANK13~16, BANK34~35 ഉൾപ്പെടെ FPGA-യുടെ ഓരോ ബാങ്കിന്റെയും e. AC7A200 FPGA കോർ ബോർഡിൽ, BANK34, BANK35 എന്നിവ DDR3-ലേക്ക് ബന്ധിപ്പിക്കേണ്ടതുണ്ട്.tagബാങ്കിന്റെ ഇ കണക്ഷൻ 1.5V ആണ്, വോളിയംtagമറ്റ് ബാങ്കിന്റെ ഇ 3.3V ആണ്. BANK15-ന്റെയും BANK16-ന്റെയും VCCO, LDO ആണ് പവർ ചെയ്യുന്നത്, LDO ചിപ്പ് മാറ്റിസ്ഥാപിച്ച് ഇത് മാറ്റാവുന്നതാണ്. VMGTAVCC ആണ് വിതരണ വോള്യംtag1.0V-ലേക്ക് ബന്ധിപ്പിച്ചിരിക്കുന്ന FPGA ആന്തരിക GTP ട്രാൻസ്സീവറിന്റെ ഇ; VMGTAVTT ആണ് അവസാനിപ്പിക്കൽ വോളിയംtag1.2V-ലേക്ക് കണക്റ്റ് ചെയ്തിരിക്കുന്ന GTP ട്രാൻസ്സീവറിന്റെ ഇ.

ആർട്ടിക്സ്-7 എഫ്പിജിഎ സിസ്റ്റത്തിന് പവർ-അപ്പ് സീക്വൻസ് VCCINT, തുടർന്ന് VCCBRAM, തുടർന്ന് VCCAUX, ഒടുവിൽ VCCO എന്നിവയുടെ പവർ ആയിരിക്കണം. VCCINT-നും VCCBRAM-നും ഒരേ വോള്യം ഉണ്ടെങ്കിൽtagഇ, അവ ഒരേ സമയം പവർ അപ്പ് ചെയ്യാൻ കഴിയും. അധികാരത്തിന്റെ ക്രമം outages വിപരീതമാണ്. GTP ട്രാൻസ്സീവറിന്റെ പവർ-അപ്പ് സീക്വൻസ് VCCINT, തുടർന്ന് VMGTAVCC, തുടർന്ന് VMGTAVTT എന്നിവയാണ്. VCCINT, VMGTAVCC എന്നിവയ്ക്ക് ഒരേ വോള്യം ഉണ്ടെങ്കിൽtagഇ, അവ ഒരേ സമയം പവർ അപ്പ് ചെയ്യാൻ കഴിയും. പവർ-ഓഫ് സീക്വൻസ്, പവർ-ഓൺ സീക്വൻസിൻറെ വിപരീതമാണ്.

ഭാഗം 3: സജീവ ഡിഫറൻഷ്യൽ ക്രിസ്റ്റൽ

AC7A200 കോർ ബോർഡിൽ രണ്ട് Sitime ആക്റ്റീവ് ഡിഫറൻഷ്യൽ ക്രിസ്റ്റലുകൾ സജ്ജീകരിച്ചിരിക്കുന്നു, ഒന്ന് 200MHz ആണ്, മോഡൽ SiT9102-200.00MHz ആണ്, FPGA-നുള്ള സിസ്റ്റം പ്രധാന ക്ലോക്ക്, DDR3 കൺട്രോൾ ക്ലോക്ക് സൃഷ്ടിക്കാൻ ഉപയോഗിക്കുന്നു; മറ്റൊന്ന് 125MHz ആണ്, മോഡൽ SiT9102 -125MHz ആണ്, GTP ട്രാൻസ്സീവറുകൾക്കുള്ള റഫറൻസ് ക്ലോക്ക് ഇൻപുട്ട്.

ഭാഗം 3.1: 200Mhz സജീവ ഡിഫറൻഷ്യൽ ക്ലോക്ക്

ചിത്രം 1-3 ലെ G1 എന്നത് ഡെവലപ്മെന്റ് ബോർഡ് സിസ്റ്റം ക്ലോക്ക് ഉറവിടം നൽകുന്ന 200M സജീവ ഡിഫറൻഷ്യൽ ക്രിസ്റ്റലാണ്. ക്രിസ്റ്റൽ ഔട്ട്പുട്ട് FPGA-യുടെ BANK34 ഗ്ലോബൽ ക്ലോക്ക് പിൻ MRCC (R4, T4) യുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു. ഈ 200Mhz ഡിഫറൻഷ്യൽ ക്ലോക്ക് FPGA-യിൽ ഉപയോക്തൃ ലോജിക്ക് പ്രവർത്തിപ്പിക്കാൻ ഉപയോഗിക്കാം. വ്യത്യസ്ത ആവൃത്തികളുടെ ക്ലോക്കുകൾ സൃഷ്ടിക്കാൻ ഉപയോക്താക്കൾക്ക് എഫ്പിജിഎയ്ക്കുള്ളിൽ പിഎൽഎൽ-കളും ഡിസിഎമ്മുകളും കോൺഫിഗർ ചെയ്യാനാകും.

ചിത്രം 3-1: 200Mhz ആക്ടീവ് ഡിഫറൻഷ്യൽ ക്രിസ്റ്റൽ സ്കീമാറ്റിക്

ചിത്രം 3-2: കോർ ബോർഡിൽ 200Mhz സജീവ ഡിഫറൻഷ്യൽ ക്രിസ്റ്റൽ

200Mhz ഡിഫറൻഷ്യൽ ക്ലോക്ക് പിൻ അസൈൻമെന്റ്

| സിഗ്നൽ നാമം | FPGA പിൻ |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

ഭാഗം 3.2: 125MHz ആക്ടീവ് ഡിഫറൻഷ്യൽ ക്രിസ്റ്റൽ

ചിത്രം 2-3-ലെ G3 എന്നത് 125MHz ആക്ടീവ് ഡിഫറൻഷ്യൽ ക്രിസ്റ്റലാണ്, ഇത് FPGA-യ്ക്കുള്ളിലെ GTP മൊഡ്യൂളിന് നൽകിയിരിക്കുന്ന റഫറൻസ് ഇൻപുട്ട് ക്ലോക്ക് ആണ്. ക്രിസ്റ്റൽ ഔട്ട്പുട്ട് FPGA-യുടെ GTP BANK216 ക്ലോക്ക് പിന്നുകളായ MGTREFCLK0P (F6), MGTREFCLK0N (E6) എന്നിവയുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു.

ചിത്രം 3-3: 125MHz ആക്ടീവ് ഡിഫറൻഷ്യൽ ക്രിസ്റ്റൽ സ്കീമാറ്റിക്

ചിത്രം 3-4: കോർ ബോർഡിൽ 125MHz സജീവ ഡിഫറൻഷ്യൽ ക്രിസ്റ്റൽ

125MHz ഡിഫറൻഷ്യൽ ക്ലോക്ക് പിൻ അസൈൻമെന്റ്

| നെറ്റ് പേര് | FPGA പിൻ |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

ഭാഗം 4: DDR3 DRAM

FPGA കോർ ബോർഡ് AC7A200 രണ്ട് മൈക്രോൺ 4Gbit (512MB) DDR3 ചിപ്പുകൾ കൊണ്ട് സജ്ജീകരിച്ചിരിക്കുന്നു (ആകെ 8Gbit), മോഡൽ MT41J256M16HA-125 ആണ് (MT41K256M16HA-125 ന് അനുയോജ്യം). DDR3 SDRAM-ന് പരമാവധി പ്രവർത്തന വേഗത 400MHz ആണ് (ഡാറ്റ നിരക്ക് 800Mbps). DDR3 മെമ്മറി സിസ്റ്റം FPGA-യുടെ BANK 34, BANK35 എന്നിവയുടെ മെമ്മറി ഇന്റർഫേസുമായി നേരിട്ട് ബന്ധിപ്പിച്ചിരിക്കുന്നു. DDR3 SDRAM-ന്റെ നിർദ്ദിഷ്ട കോൺഫിഗറേഷൻ പട്ടിക 4-1-ൽ കാണിച്ചിരിക്കുന്നു.

| ബിറ്റ് നമ്പർ | ചിപ്പ് മോഡൽ | ശേഷി | ഫാക്ടറി |

| U5,U6 | MT41J256M16HA-125 | 256M x 16ബിറ്റ് | മൈക്രോൺ |

പട്ടിക 4-1: DDR3 SDRAM കോൺഫിഗറേഷൻ

DDR3-ന്റെ ഹാർഡ്വെയർ രൂപകൽപ്പനയ്ക്ക് സിഗ്നൽ സമഗ്രതയുടെ കർശനമായ പരിഗണന ആവശ്യമാണ്. DDR3 ന്റെ ഉയർന്ന വേഗതയും സുസ്ഥിരവുമായ പ്രവർത്തനം ഉറപ്പാക്കാൻ സർക്യൂട്ട് ഡിസൈനിലെയും PCB ഡിസൈനിലെയും പൊരുത്തപ്പെടുന്ന റെസിസ്റ്റർ/ടെർമിനൽ റെസിസ്റ്റൻസ്, ട്രെയ്സ് ഇംപെഡൻസ് നിയന്ത്രണം, ട്രെയ്സ് ലെങ്ത് കൺട്രോൾ എന്നിവ ഞങ്ങൾ പൂർണ്ണമായി പരിഗണിച്ചു. ചിത്രം 4-1 DDR3 DRAM-ന്റെ ഹാർഡ്വെയർ കണക്ഷൻ വിശദമാക്കുന്നു

ചിത്രം 4-1: DDR3 DRAM സ്കീമാറ്റിക്

ചിത്രം 4-2: കോർ ബോർഡിലെ DDR3

DDR3 DRAM പിൻ അസൈൻമെന്റ്:

| നെറ്റ് പേര് | FPGA പിൻ പേര് | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

ഭാഗം 5: QSPI ഫ്ലാഷ്

FPGA കോർ ബോർഡ് AC7A200 ഒരു 128Mbit QSPI ഫ്ലാഷ് കൊണ്ട് സജ്ജീകരിച്ചിരിക്കുന്നു, കൂടാതെ മോഡൽ N25Q128 ആണ്, ഇത് 3.3V CMOS വോളിയം ഉപയോഗിക്കുന്നു.tagഇ സ്റ്റാൻഡേർഡ്. QSPI ഫ്ലാഷിന്റെ അസ്ഥിര സ്വഭാവം കാരണം, സിസ്റ്റത്തിന്റെ ബൂട്ട് ഇമേജ് സംഭരിക്കുന്നതിന് സിസ്റ്റത്തിനുള്ള ഒരു ബൂട്ട് ഉപകരണമായി ഇത് ഉപയോഗിക്കാം. ഈ ചിത്രങ്ങളിൽ പ്രധാനമായും FPGA ബിറ്റ് ഉൾപ്പെടുന്നു files, ARM ആപ്ലിക്കേഷൻ കോഡ്, സോഫ്റ്റ് കോർ ആപ്ലിക്കേഷൻ കോഡ്, മറ്റ് ഉപയോക്തൃ ഡാറ്റ fileഎസ്. SPI ഫ്ലാഷിന്റെ നിർദ്ദിഷ്ട മോഡലുകളും അനുബന്ധ പാരാമീറ്ററുകളും പട്ടിക 5-1 ൽ കാണിച്ചിരിക്കുന്നു.

| സ്ഥാനം | മോഡൽ | ശേഷി | ഫാക്ടറി |

| U8 | N25Q128 | 128M ബിറ്റ് | ന്യൂമോണിക്സ് |

പട്ടിക 5-1: QSPI ഫ്ലാഷ് സ്പെസിഫിക്കേഷൻ

FPGA ചിപ്പിന്റെ BANK0, BANK14 എന്നിവയുടെ സമർപ്പിത പിന്നുകളിലേക്ക് QSPI ഫ്ലാഷ് ബന്ധിപ്പിച്ചിരിക്കുന്നു. ക്ലോക്ക് പിൻ BANK0-ന്റെ CCLK0-ലേക്ക് കണക്റ്റ് ചെയ്തിരിക്കുന്നു, കൂടാതെ മറ്റ് ഡാറ്റയും ചിപ്പ് തിരഞ്ഞെടുത്ത സിഗ്നലുകളും യഥാക്രമം BANK00-ന്റെ D03~D14, FCS പിന്നുകളിലേക്ക് ബന്ധിപ്പിച്ചിരിക്കുന്നു. QSPI ഫ്ലാഷിന്റെ ഹാർഡ്വെയർ കണക്ഷൻ ചിത്രം 5-1 കാണിക്കുന്നു.

ചിത്രം 5-1: QSPI ഫ്ലാഷ് സ്കീമാറ്റിക്

QSPI ഫ്ലാഷ് പിൻ അസൈൻമെന്റുകൾ:

| നെറ്റ് പേര് | FPGA പിൻ പേര് | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

ചിത്രം 5-2: കോർ ബോർഡിൽ QSPI ഫ്ലാഷ്

ഭാഗം 6: കോർ ബോർഡിൽ LED ലൈറ്റ്

AC3A7 FPGA കോർ ബോർഡിൽ 200 ചുവന്ന LED ലൈറ്റുകൾ ഉണ്ട്, അതിലൊന്ന് പവർ ഇൻഡിക്കേറ്റർ ലൈറ്റ് (PWR), ഒന്ന് കോൺഫിഗറേഷൻ LED ലൈറ്റ് (DONE), ഒന്ന് യൂസർ LED ലൈറ്റ്. കോർ ബോർഡ് പവർ ചെയ്യുമ്പോൾ, പവർ ഇൻഡിക്കേറ്റർ പ്രകാശിക്കും; FPGA കോൺഫിഗർ ചെയ്യുമ്പോൾ, കോൺഫിഗറേഷൻ LED പ്രകാശിക്കും. ഉപയോക്തൃ LED ലൈറ്റ് BANK34-ന്റെ IO-യുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു, പ്രോഗ്രാം വഴി ഉപയോക്താവിന് ലൈറ്റ് ഓണും ഓഫും നിയന്ത്രിക്കാനാകും. എപ്പോൾ ഐഒ വോള്യംtagഉപയോക്തൃ എൽഇഡിയുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നത് ഉയർന്നതാണ്, ഉപയോക്തൃ എൽഇഡി പ്രകാശിക്കുന്നു. കണക്ഷൻ ഐഒ വോള്യംtagഇ കുറവാണ്, ഉപയോക്തൃ എൽഇഡി കെടുത്തിക്കളയും. LED ലൈറ്റ് ഹാർഡ്വെയർ കണക്ഷന്റെ സ്കീമാറ്റിക് ഡയഗ്രം ചിത്രം 6-1 ൽ കാണിച്ചിരിക്കുന്നു:

ചിത്രം 6-1: കോർ ബോർഡ് സ്കീമാറ്റിക്കിൽ LED ലൈറ്റുകൾ

ചിത്രം 6-2: കോർ ബോർഡിൽ LED ലൈറ്റുകൾ

ഉപയോക്തൃ LED-കളുടെ പിൻ അസൈൻമെന്റ്

| സിഗ്നൽ നാമം | FPGA പിൻ നാമം | FPGA പിൻ നമ്പർ | വിവരണം |

| LED1 | IO_L15N_T2_DQS_34 | W5 | ഉപയോക്താവ് LED |

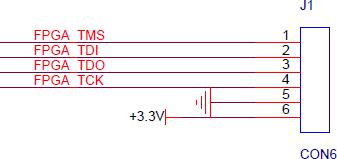

ഭാഗം 7: ജെTAG ഇൻ്റർഫേസ്

ജെTAG ടെസ്റ്റ് സോക്കറ്റ് J1, AC7A200 കോർ ബോർഡിൽ ജെTAG കോർ ബോർഡ് മാത്രം ഉപയോഗിക്കുമ്പോൾ ഡൗൺലോഡ് ചെയ്ത് ഡീബഗ്ഗിംഗ് ചെയ്യുക. ചിത്രം 7-1 എന്നത് ജെയുടെ സ്കീമാറ്റിക് ഭാഗമാണ്TAG TMS, TDI, TDO, TCK എന്നിവ ഉൾപ്പെടുന്ന പോർട്ട്. , GND, +3.3V ഈ ആറ് സിഗ്നലുകൾ.

ചിത്രം 7-1: ജെTAG ഇന്റർഫേസ് സ്കീമാറ്റിക്

ജെTAG AC1A7 FPGA കോർ ബോർഡിലെ ഇന്റർഫേസ് J200 6-പിൻ 2.54mm പിച്ച് സിംഗിൾ-വരി ടെസ്റ്റ് ഹോൾ ഉപയോഗിക്കുന്നു. നിങ്ങൾക്ക് ഉപയോഗിക്കണമെങ്കിൽ ജെTAG കോർ ബോർഡിൽ ഡീബഗ് ചെയ്യാൻ കണക്റ്റർ, നിങ്ങൾ 6-പിൻ സിംഗിൾ-വരി പിൻ ഹെഡർ സോൾഡർ ചെയ്യേണ്ടതുണ്ട്.

ചിത്രം 7-2 കാണിക്കുന്നത് ജെTAG AC1A7 FPGA കോർ ബോർഡിലെ ഇന്റർഫേസ് J200.

ചിത്രം 7-2 ജെTAG കോർ ബോർഡിലെ ഇന്റർഫേസ്

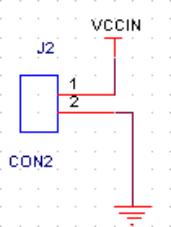

ഭാഗം 8: കോർ ബോർഡിലെ പവർ ഇന്റർഫേസ്

AC7A200 FPGA കോർ ബോർഡ് ഒറ്റയ്ക്ക് പ്രവർത്തിക്കുന്നതിന്, കോർ ബോർഡ് 2-പിൻ പവർ സപ്ലൈ ഇന്റർഫേസ് J2 റിസർവ് ചെയ്തിരിക്കുന്നു. ഉപയോക്താവിന് കോർ ബോർഡിന്റെ പ്രവർത്തനം പ്രത്യേകമായി ഡീബഗ് ചെയ്യണമെങ്കിൽ (കാരിയർ ബോർഡ് ഇല്ലാതെ), കോർ ബോർഡിലേക്ക് പവർ നൽകുന്നതിന് ബാഹ്യ ഉപകരണം +5V നൽകേണ്ടതുണ്ട്.

ചിത്രം 8-1: കോർ ബോർഡിലെ പവർ ഇന്റർഫേസ് സ്കീമാറ്റിക്

ചിത്രം 8-2: കോർ ബോർഡിലെ പവർ ഇന്റർഫേസ്

ഭാഗം 9: ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ പിൻ അസൈൻമെന്റ്

കോർ ബോർഡിൽ ആകെ നാല് ഹൈ-സ്പീഡ് ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ ഉണ്ട്.

കാരിയർ ബോർഡുമായി ബന്ധിപ്പിക്കുന്നതിന് കോർ ബോർഡ് നാല് 80-പിൻ ഇന്റർ-ബോർഡ് കണക്ടറുകൾ ഉപയോഗിക്കുന്നു. FPGA-യുടെ IO പോർട്ട് ഡിഫറൻഷ്യൽ റൂട്ടിംഗ് വഴി നാല് കണക്റ്ററുകളുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു. കണക്ടറുകളുടെ പിൻ സ്പെയ്സിംഗ് 0.5 മില്ലീമീറ്ററാണ്, ഹൈ-സ്പീഡ് ഡാറ്റാ ആശയവിനിമയത്തിനായി കാരിയർ ബോർഡിലെ കണക്റ്ററുകളിലേക്ക് ബോർഡിലേക്ക് തിരുകുക.

ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON1

80-പിൻ ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON1, VCCIN പവർ സപ്ലൈ (+5V), കാരിയർ ബോർഡിലെ ഗ്രൗണ്ട് എന്നിവയുമായി ബന്ധിപ്പിക്കാൻ ഉപയോഗിക്കുന്നു, FPGA-യുടെ സാധാരണ IO-കൾ വിപുലീകരിക്കുന്നു. CON15 ന്റെ 1 പിന്നുകൾ BANK34-ന്റെ IO പോർട്ടുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു എന്നത് ഇവിടെ ശ്രദ്ധിക്കേണ്ടതാണ്, കാരണം BANK34 കണക്ഷൻ DDR3-ലേക്ക് ബന്ധിപ്പിച്ചിരിക്കുന്നു. അതിനാൽ, വാല്യംtagഈ BANK34-ന്റെ എല്ലാ IO-കളുടെയും e നിലവാരം 1.5V ആണ്.

ബോർഡ് കണക്ടറുകളിലേക്കുള്ള ബോർഡിന്റെ പിൻ അസൈൻമെന്റ് CON1

| CON1 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

CON1 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

| പിൻ 1 | വിസിസിഐഎൻ | – | +5V | പിൻ 2 | വിസിസിഐഎൻ | – | +5V |

| പിൻ 3 | വിസിസിഐഎൻ | – | +5V | പിൻ 4 | വിസിസിഐഎൻ | – | +5V |

| പിൻ 5 | വിസിസിഐഎൻ | – | +5V | പിൻ 6 | വിസിസിഐഎൻ | – | +5V |

| പിൻ 7 | വിസിസിഐഎൻ | – | +5V | പിൻ 8 | വിസിസിഐഎൻ | – | +5V |

| പിൻ 9 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 10 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 11 | NC | – | NC | പിൻ 12 | NC | – | NC |

| പിൻ 13 | NC | – | NC | പിൻ 14 | NC | – | NC |

| പിൻ 15 | NC | – | NC | പിൻ 16 | B13_L4_P | AA15 | 3.3V |

| പിൻ 17 | NC | – | NC | പിൻ 18 | B13_L4_N | AB15 | 3.3V |

| പിൻ 19 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 20 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 21 | B13_L5_P | Y13 | 3.3V | പിൻ 22 | B13_L1_P | Y16 | 3.3V |

| പിൻ 23 | B13_L5_N | AA14 | 3.3V | പിൻ 24 | B13_L1_N | AA16 | 3.3V |

| പിൻ 25 | B13_L7_P | AB11 | 3.3V | പിൻ 26 | B13_L2_P | AB16 | 3.3V |

| പിൻ 27 | B13_L7_P | AB12 | 3.3V | പിൻ 28 | B13_L2_N | AB17 | 3.3V |

| പിൻ 29 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 30 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 31 | B13_L3_P | AA13 | 3.3V | പിൻ 32 | B13_L6_P | W14 | 3.3V |

| പിൻ 33 | B13_L3_N | AB13 | 3.3V | പിൻ 34 | B13_L6_N | Y14 | 3.3V |

| പിൻ 35 | B34_L23_P | Y8 | 1.5V | പിൻ 36 | B34_L20_P | AB7 | 1.5V |

| പിൻ 37 | B34_L23_N | Y7 | 1.5V | പിൻ 38 | B34_L20_N | AB6 | 1.5V |

| പിൻ 39 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 40 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 41 | B34_L18_N | AA6 | 1.5V | പിൻ 42 | B34_L21_N | V8 | 1.5V |

| പിൻ 43 | B34_L18_P | Y6 | 1.5V | പിൻ 44 | B34_L21_P | V9 | 1.5V |

| പിൻ 45 | B34_L19_P | V7 | 1.5V | പിൻ 46 | B34_L22_P | AA8 | 1.5V |

| പിൻ 47 | B34_L19_N | W7 | 1.5V | പിൻ 48 | B34_L22_N | AB8 | 1.5V |

| പിൻ 49 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 50 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 51 | XADC_VN | M9 | അനലോഗ് | പിൻ 52 | NC | ||

| പിൻ 53 | XADC_VP | L10 | അനലോഗ് | പിൻ 54 | B34_L25 | U7 | 1.5V |

| പിൻ 55 | NC | – | NC | പിൻ 56 | B34_L24_P | W9 | 1.5V |

| പിൻ 57 | NC | – | NC | പിൻ 58 | B34_L24_N | Y9 | 1.5V |

| പിൻ 59 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 60 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 61 | B16_L1_N | F14 | 3.3V | പിൻ 62 | NC | – | NC |

| പിൻ 63 | B16_L1_P | F13 | 3.3V | പിൻ 64 | NC | – | NC |

| പിൻ 65 | B16_L4_N | E14 | 3.3V | പിൻ 66 | NC | – | NC |

| പിൻ 67 | B16_L4_P | E13 | 3.3V | പിൻ 68 | NC | – | NC |

| പിൻ 69 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 70 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 71 | B16_L6_N | D15 | 3.3V | പിൻ 72 | NC | – | NC |

| പിൻ 73 | B16_L6_P | D14 | 3.3V | പിൻ 74 | NC | – | NC |

| പിൻ 75 | B16_L8_P | C13 | 3.3V | പിൻ 76 | NC | – | NC |

| പിൻ 77 | B16_L8_N | B13 | 3.3V | പിൻ 78 | NC | – | NC |

| പിൻ 79 | NC | – | NC | പിൻ 80 | NC | – | NC |

ചിത്രം 9-1: കോർ ബോർഡിലെ ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON1

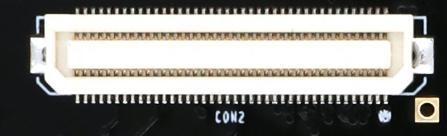

ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON2

FPGA-യുടെ BANK80, BANK2 എന്നിവയുടെ സാധാരണ IO വിപുലീകരിക്കാൻ 13-പിൻ സ്ത്രീ കണക്ഷൻ ഹെഡർ CON14 ഉപയോഗിക്കുന്നു. വോള്യംtagരണ്ട് ബാങ്കുകളുടെയും ഇ നിലവാരം 3.3V ആണ്.

ബോർഡ് കണക്ടറുകളിലേക്കുള്ള ബോർഡിന്റെ പിൻ അസൈൻമെന്റ് CON2

| CON2 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

CON2 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

| പിൻ 1 | B13_L16_P | W15 | 3.3V | പിൻ 2 | B14_L16_P | V17 | 3.3V |

| പിൻ 3 | B13_L16_N | W16 | 3.3V | പിൻ 4 | B14_L16_N | W17 | 3.3V |

| പിൻ 5 | B13_L15_P | T14 | 3.3V | പിൻ 6 | B13_L14_P | U15 | 3.3V |

| പിൻ 7 | B13_L15_N | T15 | 3.3V | പിൻ 8 | B13_L14_N | V15 | 3.3V |

| പിൻ 9 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 10 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 11 | B13_L13_P | V13 | 3.3V | പിൻ 12 | B14_L10_P | AB21 | 3.3V |

| പിൻ 13 | B13_L13_N | V14 | 3.3V | പിൻ 14 | B14_L10_N | AB22 | 3.3V |

| പിൻ 15 | B13_L12_P | W11 | 3.3V | പിൻ 16 | B14_L8_N | AA21 | 3.3V |

| പിൻ 17 | B13_L12_N | W12 | 3.3V | പിൻ 18 | B14_L8_P | AA20 | 3.3V |

| പിൻ 19 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 20 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 21 | B13_L11_P | Y11 | 3.3V | പിൻ 22 | B14_L15_N | AB20 | 3.3V |

| പിൻ 23 | B13_L11_N | Y12 | 3.3V | പിൻ 24 | B14_L15_P | AA19 | 3.3V |

| പിൻ 25 | B13_L10_P | V10 | 3.3V | പിൻ 26 | B14_L17_P | AA18 | 3.3V |

| പിൻ 27 | B13_L10_N | W10 | 3.3V | പിൻ 28 | B14_L17_N | AB18 | 3.3V |

| പിൻ 29 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 30 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 31 | B13_L9_N | AA11 | 3.3V | പിൻ 32 | B14_L6_N | T20 | 3.3V |

| പിൻ 33 | B13_L9_P | AA10 | 3.3V | പിൻ 34 | B13_IO0 | Y17 | 3.3V |

| പിൻ 35 | B13_L8_N | AB10 | 3.3V | പിൻ 36 | B14_L7_N | W22 | 3.3V |

| പിൻ 37 | B13_L8_P | AA9 | 3.3V | പിൻ 38 | B14_L7_P | W21 | 3.3V |

| പിൻ 39 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 40 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 41 | B14_L11_N | V20 | 3.3V | പിൻ 42 | B14_L4_P | T21 | 3.3V |

| പിൻ 43 | B14_L11_P | U20 | 3.3V | പിൻ 44 | B14_L4_N | U21 | 3.3V |

| പിൻ 45 | B14_L14_N | V19 | 3.3V | പിൻ 46 | B14_L9_P | Y21 | 3.3V |

| പിൻ 47 | B14_L14_P | V18 | 3.3V | പിൻ 48 | B14_L9_N | Y22 | 3.3V |

| പിൻ 49 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 50 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 51 | B14_L5_N | R19 | 3.3V | പിൻ 52 | B14_L12_N | W20 | 3.3V |

| പിൻ 53 | B14_L5_P | P19 | 3.3V | പിൻ 54 | B14_L12_P | W19 | 3.3V |

| പിൻ 55 | B14_L18_N | U18 | 3.3V | പിൻ 56 | B14_L13_N | Y19 | 3.3V |

| പിൻ 57 | B14_L18_P | U17 | 3.3V | പിൻ 58 | B14_L13_P | Y18 | 3.3V |

| പിൻ 59 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 60 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 61 | B13_L17_P | T16 | 3.3V | പിൻ 62 | B14_L3_N | V22 | 3.3V |

| പിൻ 63 | B13_L17_N | U16 | 3.3V | പിൻ 64 | B14_L3_P | U22 | 3.3V |

| പിൻ 65 | B14_L21_N | P17 | 3.3V | പിൻ 66 | B14_L20_N | T18 | 3.3V |

| പിൻ 67 | B14_L21_P | N17 | 3.3V | പിൻ 68 | B14_L20_P | R18 | 3.3V |

| പിൻ 69 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 70 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 71 | B14_L22_P | P15 | 3.3V | പിൻ 72 | B14_L19_N | R14 | 3.3V |

| പിൻ 73 | B14_L22_N | R16 | 3.3V | പിൻ 74 | B14_L19_P | P14 | 3.3V |

| പിൻ 75 | B14_L24_N | R17 | 3.3V | പിൻ 76 | B14_L23_P | N13 | 3.3V |

| പിൻ 77 | B14_L24_P | P16 | 3.3V | പിൻ 78 | B14_L23_N | N14 | 3.3V |

| പിൻ 79 | B14_IO0 | P20 | 3.3V | പിൻ 80 | B14_IO25 | N15 | 3.3V |

ചിത്രം 9-2: കോർ ബോർഡിലെ ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON2

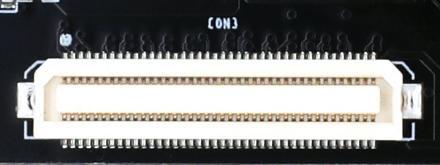

ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON3

FPGA-യുടെ BANK80, BANK3 എന്നിവയുടെ സാധാരണ IO വിപുലീകരിക്കാൻ 15-പിൻ കണക്റ്റർ CON16 ഉപയോഗിക്കുന്നു. കൂടാതെ, നാല് ജെTAG സിഗ്നലുകളും CON3 കണക്റ്റർ വഴി കാരിയർ ബോർഡുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു. വോള്യംtagBANK15, BANK16 എന്നിവയുടെ e മാനദണ്ഡങ്ങൾ ഒരു LDO ചിപ്പ് വഴി ക്രമീകരിക്കാൻ കഴിയും. സ്ഥിരമായി ഇൻസ്റ്റാൾ ചെയ്ത LDO 3.3V ആണ്. നിങ്ങൾക്ക് മറ്റ് സ്റ്റാൻഡേർഡ് ലെവലുകൾ ഔട്ട്പുട്ട് ചെയ്യണമെങ്കിൽ, അനുയോജ്യമായ ഒരു LDO ഉപയോഗിച്ച് നിങ്ങൾക്ക് അത് മാറ്റിസ്ഥാപിക്കാം.

ബോർഡ് കണക്ടറുകളിലേക്കുള്ള ബോർഡിന്റെ പിൻ അസൈൻമെന്റ് CON3

| CON3 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

CON3 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

| പിൻ 1 | B15_IO0 | J16 | 3.3V | പിൻ 2 | B15_IO25 | M17 | 3.3V |

| പിൻ 3 | B16_IO0 | F15 | 3.3V | പിൻ 4 | B16_IO25 | F21 | 3.3V |

| പിൻ 5 | B15_L4_P | G17 | 3.3V | പിൻ 6 | B16_L21_N | A21 | 3.3V |

| പിൻ 7 | B15_L4_N | G18 | 3.3V | പിൻ 8 | B16_L21_P | B21 | 3.3V |

| പിൻ 9 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 10 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 11 | B15_L2_P | G15 | 3.3V | പിൻ 12 | B16_L23_P | E21 | 3.3V |

| പിൻ 13 | B15_L2_N | G16 | 3.3V | പിൻ 14 | B16_L23_N | D21 | 3.3V |

| പിൻ 15 | B15_L12_P | J19 | 3.3V | പിൻ 16 | B16_L22_P | E22 | 3.3V |

| പിൻ 17 | B15_L12_N | H19 | 3.3V | പിൻ 18 | B16_L22_N | D22 | 3.3V |

| പിൻ 19 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 20 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 21 | B15_L11_P | J20 | 3.3V | പിൻ 22 | B16_L24_P | G21 | 3.3V |

| പിൻ 23 | B15_L11_N | J21 | 3.3V | പിൻ 24 | B16_L24_N | G22 | 3.3V |

| പിൻ 25 | B15_L1_N | G13 | 3.3V | പിൻ 26 | B15_L8_N | G20 | 3.3V |

| പിൻ 27 | B15_L1_P | H13 | 3.3V | പിൻ 28 | B15_L8_P | H20 | 3.3V |

| പിൻ 29 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 30 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 31 | B15_L5_P | J15 | 3.3V | പിൻ 32 | B15_L7_N | H22 | 3.3V |

| പിൻ 33 | B15_L5_N | H15 | 3.3V | പിൻ 34 | B15_L7_P | J22 | 3.3V |

| പിൻ 35 | B15_L3_N | H14 | 3.3V | പിൻ 36 | B15_L9_P | K21 | 3.3V |

| പിൻ 37 | B15_L3_P | J14 | 3.3V | പിൻ 38 | B15_L9_N | K22 | 3.3V |

| പിൻ 39 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 40 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 41 | B15_L19_P | K13 | 3.3V | പിൻ 42 | B15_L15_N | M22 | 3.3V |

| പിൻ 43 | B15_L19_N | K14 | 3.3V | പിൻ 44 | B15_L15_P | N22 | 3.3V |

| പിൻ 45 | B15_L20_P | M13 | 3.3V | പിൻ 46 | B15_L6_N | H18 | 3.3V |

| പിൻ 47 | B15_L20_N | L13 | 3.3V | പിൻ 48 | B15_L6_P | H17 | 3.3V |

| പിൻ 49 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 50 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 51 | B15_L14_P | L19 | 3.3V | പിൻ 52 | B15_L13_N | K19 | 3.3V |

| പിൻ 53 | B15_L14_N | L20 | 3.3V | പിൻ 54 | B15_L13_P | K18 | 3.3V |

| പിൻ 55 | B15_L21_P | K17 | 3.3V | പിൻ 56 | B15_L10_P | M21 | 3.3V |

| പിൻ 57 | B15_L21_N | J17 | 3.3V | പിൻ 58 | B15_L10_N | L21 | 3.3V |

| പിൻ 59 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 60 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 61 | B15_L23_P | L16 | 3.3V | പിൻ 62 | B15_L18_P | N20 | 3.3V |

| പിൻ 63 | B15_L23_N | K16 | 3.3V | പിൻ 64 | B15_L18_N | M20 | 3.3V |

| പിൻ 65 | B15_L22_P | L14 | 3.3V | പിൻ 66 | B15_L17_N | N19 | 3.3V |

| പിൻ 67 | B15_L22_N | L15 | 3.3V | പിൻ 68 | B15_L17_P | N18 | 3.3V |

| പിൻ 69 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 70 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 71 | B15_L24_P | M15 | 3.3V | പിൻ 72 | B15_L16_P | M18 | 3.3V |

| പിൻ 73 | B15_L24_N | M16 | 3.3V | പിൻ 74 | B15_L16_N | L18 | 3.3V |

| പിൻ 75 | NC | – | പിൻ 76 | NC | – | ||

| പിൻ 77 | FPGA_TCK | V12 | 3.3V | പിൻ 78 | FPGA_TDI | R13 | 3.3V |

| പിൻ 79 | FPGA_TDO | U13 | 3.3V | പിൻ 80 | FPGA_TMS | T13 | 3.3V |

ചിത്രം 9-3: കോർ ബോർഡിലെ ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON3

ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON4

FPGA BANK80-ന്റെ സാധാരണ IO, GTP ഹൈ-സ്പീഡ് ഡാറ്റയും ക്ലോക്ക് സിഗ്നലുകളും വിപുലീകരിക്കാൻ 4-പിൻ കണക്റ്റർ CON16 ഉപയോഗിക്കുന്നു. വോള്യംtagBANK16-ന്റെ IO പോർട്ടിന്റെ ഇ നിലവാരം ഒരു LDO ചിപ്പ് ഉപയോഗിച്ച് ക്രമീകരിക്കാവുന്നതാണ്. സ്ഥിരമായി ഇൻസ്റ്റാൾ ചെയ്ത LDO 3.3V ആണ്. ഉപയോക്താവിന് മറ്റ് സ്റ്റാൻഡേർഡ് ലെവലുകൾ ഔട്ട്പുട്ട് ചെയ്യാൻ താൽപ്പര്യമുണ്ടെങ്കിൽ, അത് അനുയോജ്യമായ ഒരു LDO ഉപയോഗിച്ച് മാറ്റിസ്ഥാപിക്കാം. GTP-യുടെ ഹൈ-സ്പീഡ് ഡാറ്റയും ക്ലോക്ക് സിഗ്നലുകളും കോർ ബോർഡിൽ കർശനമായി വ്യത്യാസപ്പെട്ടിരിക്കുന്നു. ഡാറ്റ ലൈനുകളുടെ നീളം തുല്യമാണ് കൂടാതെ സിഗ്നൽ ഇടപെടൽ തടയുന്നതിന് ഒരു നിശ്ചിത ഇടവേളയിൽ സൂക്ഷിക്കുന്നു.

ബോർഡ് കണക്ടറുകളിലേക്കുള്ള ബോർഡിന്റെ പിൻ അസൈൻമെന്റ് CON4

| CON4 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

CON4 പിൻ |

നെറ്റ് പേര് |

FPGA പിൻ |

വാല്യംtage ലെവൽ |

| പിൻ 1 | NC | – | – | പിൻ 2 | – | – | |

| പിൻ 3 | NC | – | – | പിൻ 4 | – | – | |

| പിൻ 5 | NC | – | – | പിൻ 6 | – | – | |

| പിൻ 7 | NC | – | – | പിൻ 8 | – | – | |

| പിൻ 9 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 10 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 11 | NC | – | – | പിൻ 12 | MGT_TX2_P | B6 | വ്യത്യാസം |

| പിൻ 13 | NC | – | – | പിൻ 14 | MGT_TX2_N | A6 | വ്യത്യാസം |

| പിൻ 15 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 16 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 17 | MGT_TX3_P | D7 | വ്യത്യാസം | പിൻ 18 | MGT_RX2_P | B10 | വ്യത്യാസം |

| പിൻ 19 | MGT_TX3_N | C7 | വ്യത്യാസം | പിൻ 20 | MGT_RX2_N | A10 | വ്യത്യാസം |

| പിൻ 21 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 22 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 23 | MGT_RX3_P | D9 | വ്യത്യാസം | പിൻ 24 | MGT_TX0_P | B4 | വ്യത്യാസം |

| പിൻ 25 | MGT_RX3_N | C9 | വ്യത്യാസം | പിൻ 26 | MGT_TX0_N | A4 | വ്യത്യാസം |

| പിൻ 27 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 28 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 29 | MGT_TX1_P | D5 | വ്യത്യാസം | പിൻ 30 | MGT_RX0_P | B8 | വ്യത്യാസം |

| പിൻ 31 | MGT_TX1_N | C5 | വ്യത്യാസം | പിൻ 32 | MGT_RX0_N | A8 | വ്യത്യാസം |

| പിൻ 33 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 34 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 35 | MGT_RX1_P | D11 | വ്യത്യാസം | പിൻ 36 | MGT_CLK1_P | F10 | വ്യത്യാസം |

| പിൻ 37 | MGT_RX1_N | C11 | വ്യത്യാസം | പിൻ 38 | MGT_CLK1_N | E10 | വ്യത്യാസം |

| പിൻ 39 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 40 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 41 | B16_L5_P | E16 | 3.3V | പിൻ 42 | B16_L2_P | F16 | 3.3V |

| പിൻ 43 | B16_L5_N | D16 | 3.3V | പിൻ 44 | B16_L2_N | E17 | 3.3V |

| പിൻ 45 | B16_L7_P | B15 | 3.3V | പിൻ 46 | B16_L3_P | C14 | 3.3V |

| പിൻ 47 | B16_L7_N | B16 | 3.3V | പിൻ 48 | B16_L3_N | C15 | 3.3V |

| പിൻ 49 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 50 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 51 | B16_L9_P | A15 | 3.3V | പിൻ 52 | B16_L10_P | A13 | 3.3V |

| പിൻ 53 | B16_L9_N | A16 | 3.3V | പിൻ 54 | B16_L10_N | A14 | 3.3V |

| പിൻ 55 | B16_L11_P | B17 | 3.3V | പിൻ 56 | B16_L12_P | D17 | 3.3V |

| പിൻ 57 | B16_L11_N | B18 | 3.3V | പിൻ 58 | B16_L12_N | C17 | 3.3V |

| പിൻ 59 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 60 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 61 | B16_L13_P | C18 | 3.3V | പിൻ 62 | B16_L14_P | E19 | 3.3V |

| പിൻ 63 | B16_L13_N | C19 | 3.3V | പിൻ 64 | B16_L14_N | D19 | 3.3V |

| പിൻ 65 | B16_L15_P | F18 | 3.3V | പിൻ 66 | B16_L16_P | B20 | 3.3V |

| പിൻ 67 | B16_L15_N | E18 | 3.3V | പിൻ 68 | B16_L16_N | A20 | 3.3V |

| പിൻ 69 | ജിഎൻഡി | – | ഗ്രൗണ്ട് | പിൻ 70 | ജിഎൻഡി | – | ഗ്രൗണ്ട് |

| പിൻ 71 | B16_L17_P | A18 | 3.3V | പിൻ 72 | B16_L18_P | F19 | 3.3V |

| പിൻ 73 | B16_L17_N | A19 | 3.3V | പിൻ 74 | B16_L18_N | F20 | 3.3V |

| പിൻ 75 | B16_L19_P | D20 | 3.3V | പിൻ 76 | B16_L20_P | C22 | 3.3V |

| പിൻ 77 | B16_L19_N | C20 | 3.3V | പിൻ 78 | B16_L20_N | B22 | 3.3V |

| പിൻ 79 | NC | – | പിൻ 80 | NC | – |

ചിത്രം 9-4: കോർ ബോർഡിലെ ബോർഡ് ടു ബോർഡ് കണക്ടറുകൾ CON4

ഭാഗം 10: പവർ സപ്ലൈ

AC7A200 FPGA കോർ ബോർഡ് DC5V കാരിയർ ബോർഡ് വഴിയാണ് നൽകുന്നത്, മാത്രമല്ല ഇത് ഒറ്റയ്ക്ക് ഉപയോഗിക്കുമ്പോൾ മിനി USB ഇന്റർഫേസാണ് നൽകുന്നത്. കേടുപാടുകൾ ഒഴിവാക്കാൻ, മിനി യുഎസ്ബിയും കാരിയർ ബോർഡും ഒരേ സമയം വൈദ്യുതി നൽകാതിരിക്കാൻ ശ്രദ്ധിക്കുക. ബോർഡിലെ പവർ സപ്ലൈ ഡിസൈൻ ഡയഗ്രം ചിത്രം 10-1 ൽ കാണിച്ചിരിക്കുന്നു.

ചിത്രം 10-1: കോർ ബോർഡ് സ്കീമാറ്റിക്കിൽ പവർ സപ്ലൈ

കോർ ബോർഡ് +5V പവർ ചെയ്യുകയും മൂന്ന് DC/DC പവർ സപ്ലൈ ചിപ്പ് TLV3.3RGT വഴി +1.5V, +1.8V, +1.0V, +62130V ഫോർ-വേ പവർ സപ്ലൈ ആയി പരിവർത്തനം ചെയ്യുകയും ചെയ്യുന്നു. +1.0V യുടെ കറന്റ് 6A വരെയും മറ്റ് മൂന്ന് ഔട്ട്പുട്ട് വൈദ്യുതധാരകൾ 3A വരെയും ആകാം. ഒരു LDOSPX3819M5-3-3 ആണ് VCCIO സൃഷ്ടിക്കുന്നത്. VCCIO പ്രധാനമായും FPGA-യുടെ BANK15, BANK16 എന്നിവയിലേക്കാണ് വൈദ്യുതി നൽകുന്നത്. ഉപയോക്താക്കൾക്ക് BANK15,16-ന്റെ IO വ്യത്യസ്ത വോള്യങ്ങളിലേക്ക് മാറ്റാനാകുംtagഅവരുടെ LDO ചിപ്പ് മാറ്റിസ്ഥാപിച്ചുകൊണ്ട് ഇ മാനദണ്ഡങ്ങൾ. 1.5V VTT, VREF വോളിയം സൃഷ്ടിക്കുന്നുtagTI-യുടെ TPS3 വഴി DDR51200 ആവശ്യപ്പെടുന്നു. GTP ട്രാൻസ്സിവറിനായുള്ള MGTAVTT, MGTAVCC എന്നിവയുടെ 1.8V പവർ സപ്ലൈ TI-യുടെ TPS74801 ചിപ്പിൽ നിന്നാണ് ഉത്പാദിപ്പിക്കുന്നത്. ഓരോ വൈദ്യുതി വിതരണത്തിന്റെയും പ്രവർത്തനങ്ങൾ ഇനിപ്പറയുന്ന പട്ടികയിൽ കാണിച്ചിരിക്കുന്നു:

| വൈദ്യുതി വിതരണം | ഫംഗ്ഷൻ |

| +1.0V | FPGA കോർ വോളിയംtage |

| +1.8V | FPGA ഓക്സിലറി വാല്യംtage, TPS74801 വൈദ്യുതി വിതരണം |

| +3.3V | FPGA-യുടെ ബാങ്ക്0, ബാങ്ക്13, ബാങ്ക്14 എന്നിവയുടെ VCCIO, QSIP ഫ്ലാഷ്, ക്ലോക്ക് ക്രിസ്റ്റൽ |

| +1.5V | FPGA-യുടെ DDR3, Bank34, Bank35 |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA ബാങ്ക്15, ബാങ്ക്16 |

| MGTAVTT(+1.2V) | FPGA-യുടെ GTP ട്രാൻസ്സിവർ ബാങ്ക്216 |

| MGTVCC(+1.0V) | FPGA-യുടെ GTP ട്രാൻസ്സിവർ ബാങ്ക്216 |

Artix-7 FPGA-യുടെ പവർ സപ്ലൈക്ക് പവർ-ഓൺ സീക്വൻസ് ആവശ്യകത ഉള്ളതിനാൽ, സർക്യൂട്ട് ഡിസൈനിൽ, ചിപ്പിന്റെ പവർ ആവശ്യകതകൾക്കനുസൃതമായി ഞങ്ങൾ രൂപകൽപ്പന ചെയ്തിട്ടുണ്ട്, കൂടാതെ പവർ-ഓൺ 1.0V->1.8V->(1.5) ആണ്. V, 3.3V, VCCIO) കൂടാതെ 1.0V-> MGTAVCC -> MGTAVTT, ചിപ്പിന്റെ സാധാരണ പ്രവർത്തനം ഉറപ്പാക്കുന്നതിനുള്ള സർക്യൂട്ട് ഡിസൈൻ.

AC7A200 FPGA കോർ ബോർഡിലെ പവർ സർക്യൂട്ട് ചിത്രം 10-2 ൽ കാണിച്ചിരിക്കുന്നു:

ചിത്രം 10-2: AC7A200 FPGA കോർ ബോർഡിലെ പവർ സപ്ലൈ

ഭാഗം 11: വലിപ്പത്തിന്റെ അളവ്

ചിത്രം 11-1: AC7A200 FPGA കോർ ബോർഡ് (മുകളിൽ View)

ചിത്രം 11-2: AC7A200 FPGA കോർ ബോർഡ് (ചുവടെ View)

പ്രമാണങ്ങൾ / വിഭവങ്ങൾ

|

ALINX AC7A200 ARTIX-7 FPGA ഡെവലപ്മെന്റ് ബോർഡ് [pdf] ഉപയോക്തൃ മാനുവൽ AC7A200 ARTIX-7 FPGA ഡെവലപ്മെന്റ് ബോർഡ്, AC7A200, ARTIX-7 FPGA ഡെവലപ്മെന്റ് ബോർഡ്, FPGA ഡവലപ്മെന്റ് ബോർഡ്, ഡെവലപ്മെന്റ് ബോർഡ്, ബോർഡ് |